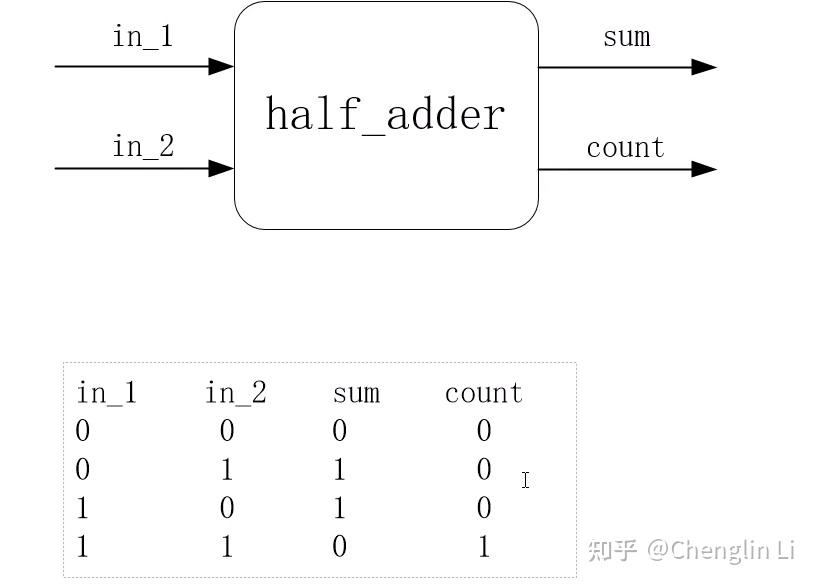

FPGA学习笔记(二)Verilog实现半加器

1 参考资料

Verilog中assign的使用_ascend__a1的博客-CSDN博客_assign verilog

2 计算程序

/*

assign相当于连线,一般是将一个变量的值不间断地赋值给另一个变量,就像把这两个变量连在一起,所以习惯性的当做连线用,比如把一个模块的输出给另一个模块当输入。

assign的功能属于组合逻辑的范畴,应用范围可概括为以下三点:

(1)持续赋值;

(2)连线;

(3)对wire型变量赋值,wire是线网,相当于实际的连接线,如果要用assign直接连接,就用wire型变量。wire型变量的值随时变化。其实以上三点是相通的。

要更好的把握assign的使用,Verilog中有几个要点需要深入理解和掌握:

(1)在Verilog module中的所有过程块(如initial块和always块)、连续赋值语句(如assign语句)和实例引用都是并行的。在同一module中这三者出现的先后顺序没有关系。

(2)只有连续赋值语句assign和实例引用语句可以独立于过程块而存在于module的功能定义部分。

(3)连续赋值assign语句独立于过程块,所以不能在always过程块中使用assign语句。

————————————————

版权声明:本文为CSDN博主「ascend__a1」的原创文章,遵循CC 4.0 BY-SA版权协议,转载请附上原文出处链接及本声明。

原文链接:https://blog.csdn.net/avrmcu1/article/details/13024229

module Add(

input in_1,

input in_2,

output sum,

output count

assign {count, sum}=in_1+in_2;

endmodule3 Testbench文件

// Simulation tool : ModelSim (Verilog)

`timescale 1 ns/ 1 ps

module Add_tb();

reg in_1;

reg in_2;

// wires

wire count;

wire sum;

// assign statements (if any)

Add Add_entity (

// port map - connection between master ports and signals/registers

.count(count),

.in_1(in_1),

.in_2(in_2),

.sum(sum)

initial

begin

in_1=1'b0;

in_2=1'b1;

always

begin

#3 in_1=~in_1;